PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity comparator is port( a : in STD_LOGIC; b : in STD_LOGIC; equal : out STD_LOGIC; lower : out STD_LOGIC; greater : out STD_LOGIC );end comparator;architecture comparator_arc of comparator isbegin equal <= a xnor b; lower <= (not a) and b; greater <= a and (not b);end comparator_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity full_subtractor is port( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; difference : out STD_LOGIC; borrow : out STD_LOGIC );end full_subtractor;architecture full_subtractor_arc of full_subtractor isbegin difference <= a xor b xor c; borrow <= ((not a) and b) or (b and c) or (c and (not a));end full_subtractor_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity half_subtractor is port( a : in STD_LOGIC; b : in STD_LOGIC; diff : out STD_LOGIC; borrow : out STD_LOGIC );end half_subtractor;architecture half_subtractor_arc of half_subtractor isbegin diff <= a xor b; borrow <= (not a) and b;end half_subtractor_arc;

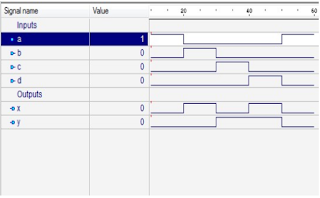

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity encoder4_2 is port( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; d : in STD_LOGIC; x : out STD_LOGIC; y : out STD_LOGIC );end encoder4_2; architecture encoder4_2_arc of encoder4_2 isbegin x <= b or d; y <= c or d;end encoder4_2_arc;

PROGRAM :

library IEEE;use IEEE.STD_LOGIC_1164.all;entity decoder2_4 is port( a : in STD_LOGIC; b : in STD_LOGIC; w : out STD_LOGIC; x : out STD_LOGIC; y : out STD_LOGIC; z : out STD_LOGIC );end decoder2_4;architecture decoder2_4_arc of decoder2_4 isbegin w <= (not a) and (not b); x <= (not a) and b; y <= (a and (not b)); z <= a and b;end decoder2_4_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity multiplexer_4_1 is port( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; d : in STD_LOGIC; x : in STD_LOGIC; y : in STD_LOGIC; dout : out STD_LOGIC );end multiplexer_4_1;architecture multiplexer_4_1_arc of multiplexer_4_1 isbegin dout <= ((not x) and (not y) and a) or ((not x) and y and b) or (x and (not y) and c) or (x and y and d);end multiplexer_4_1_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity multiplexer_4_1 is port( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; d : in STD_LOGIC; x : in STD_LOGIC; y : in STD_LOGIC; dout : out STD_LOGIC );end multiplexer_4_1;architecture multiplexer_4_1_arc of multiplexer_4_1 isbegin dout <= ((not x) and (not y) and a) or ((not x) and y and b) or (x and (not y) and c) or (x and y and d);end multiplexer_4_1_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity Full_Adder_Design is port( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; sum : out STD_LOGIC; carry : out STD_LOGIC );end Full_Adder_Design;architecture Full_Adder_Design_arc of Full_Adder_Design isbegin sum <= a xor b xor c; carry <= (a and b) or (b and c) or (c and a); end Full_Adder_Design_arc;

PROGRAM:

library IEEE;use IEEE.STD_LOGIC_1164.all;entity Half_Adder is port( a : in STD_LOGIC; b : in STD_LOGIC; sum : out STD_LOGIC; carry : out STD_LOGIC );end Half_Adder;architecture Half_Adder_arc of Half_Adder isbegin sum <= a xor b; carry <= a and b;end Half_Adder_arc;

Program -library IEEE;use IEEE.STD_LOGIC_1164.all;entity and_gate is port( a : in STD_LOGIC; b : in STD_LOGIC; dout : out STD_LOGIC );end and_gate;architecture and_gate_arc of and_gate isbegin dout <= a and b;end and_gate_arc;